|

收藏到会员中心

|

| 文档题目: |

等精度频率计的设计 |

|

| 上传会员: |

wate010 |

| 提交日期: |

2013-10-18 13:15:22 |

| 文档分类: |

电子信息机电 |

| 浏览次数: |

21 |

| 下载次数: |

0

次 |

|

|

| 下载地址: |

等精度频率计的设计 (需要:198 积分) 如何获取积分? 等精度频率计的设计 (需要:198 积分) 如何获取积分? |

| 下载提示: |

不支持迅雷等下载工具,请右键另存为下载,或用浏览器下载。不退出登录1小时内重复下载不扣积分。

|

| 文档介绍: |

以下为文档部分内容,全文可通过注册成本站会员下载获取。也可加管理员微信/QQ:17304545代下载。

|

| 文档字数: |

|

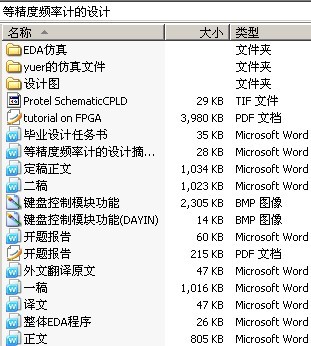

文档字数:17199 摘 要 测量以频率为参数的被测信号,通常采用的是测频法或测周法。但是,当频率变化较大,如范围为100Hz~100KHz时,测频法和测周法就存在着很大的局限性,难以实现宽频带、高精度的测量。所以,当要求有一种测频方法能对频率变化范围较大的信号进行高精度的测量时,就必须采用等精度的测频技术。 等精度频率计是一种能够高精度地测量被测信号频率的数字测量仪器。它被广泛应用于航天、航空、电子、测控、自动化测量等领域。本论文利用等精度频率测量的原理,达到设计等精度频率计的目的。由于Altera公司生产的复杂可编程逻辑(CPLD)EPM7128具有定时精确及速度快等特点;同时,因为涉及到的倒数运算(频率与周期互为倒数关系),在单片机AT89C51上运算会非常简单方便。所以,硬件方面主要由以上两部分组成。软件方面,用VHDL语言编程在MAX+PLUSII中完成CPLD的软件设计、编译、调试、仿真以及下载;其中,单片机AT89C51是系统的主控部件。 系统中,采用十进制数字显示,实现测量正弦信号,方波信号,尖脉冲信号的频率、周期等的基本功能, CPLD与单片机相互结合、取长补短,以达到最佳的效果。 关键词:等精度频率计 CPLD/FPGA VHDL 显示电路

目 录 第1章 绪论 1 1.1 课题分析 1 1.2 等精度频率计的背景 1 1.3 VHDL语言和Max+Plus II环境简介 3 1.4 课题要求 4 第2章 方案选择及各部件的原理分析 6 2.1 总体方案比较 6 2.2 等精度频率计的测频原理 8 2.2.1频率的测量原理 8 2.2.2 周期的测量原理 9 2.2.3 脉宽的测量原理 10 2.2.4 占空比的测量原理 10 2.2.5 标准频率的发生装置 10 2.3 系统设计方案以及主要组成部分 10 第3章 硬件部分的设计 12 3.1可编辑逻辑器件(CPLD)和AT89C51简介 12 3.1.1 可编辑逻辑器件(CPLD)简介 12 3.1.2 AT89C51单片机简介 14 3.2 等精度频率计各模块功能及电路图 15 3.2.1 键盘控制模块功能 15 3.2.2 显示电路模块功能 16 3.2.3 单片机模块功能 18 3.2.4 信号输入放大和整形模块及其功能 20 第4章 软件设计 21 4.1 CPLD模块的软件设计 21 4.1.1 VHDL语言优点 21 4.1.2 采用VHDL语言设计系统的特点 22 4.1.3 各信号的定义、系统的总体程序及仿真波形图 22 4.1.4 测频和测周期的实现 25 4.1.5测量脉冲宽度和占空比模块的设计 26 4.2 单片机模块程序设计 28 第5章 社会效益及经济效益分析 35 结论 36 致谢 37 参考文献 38 附录Ⅰ 元器件清单 40 附录Ⅱ 程序清单 41 附录Ⅲ 电路原理图 56

| (本文由word文档网(www.wordocx.com)会员上传,如需要全文请注册成本站会员下载) |

|

|

|